This post will review 2 llm options in emacs how I set them up.

Ellama

From ellama

Ellama is a tool for interacting with large language models from Emacs. It allows you to ask questions and receive responses from the LLMs. Ellama can perform various tasks such as translation, code review, summarization, enhancing grammar/spelling or wording and more through the Emacs interface. Ellama natively supports streaming output, making it effortless to use with your preferred text editor.

rtimer: Writing a Timer with Aider

Aider + Claude Sonnet 3.5

This morning, I needed a timer to spend only 10 minutes reading a book. I searched for CLI tools but couldn't find anything immediately that suited my needs due to laziness. So, I decided to write one myself with the help of AI.

Using Aider coupled with Claude Sonnet 3.5, I was able to get something working on the first try. Afterward, I added a few features:

A comparison between open source host firmware solutions and closed source UEFI

This whitepaper makes the case that UEFI firmware and more specifically EDK2 based solutions, be it open or the more ubiquitous closed ones, hurt business by driving up cost and delaying time to market, while at the same time are the root cause of more and more security problems. This whitepaper will contrast this UEFI status quo with other existing solutions like LinuxBoot in combination with coreboot, which fully embrace open source development, are scoring better on all those metrics. This is both due to design decisions and the related development models.

Integrating rust in coreboot: baby steps

Rust in coreboot?

Rust is a programming language with emphasis on performance, type safety and concurrency. It enforces memory safety at compile time. Unlike the C standard which is a 700+ page document, with a LOT of documented undefined behavior, rust has no undefined behavior unless the unsafe keyword is used. Zero cost abstractions make rust binaries very efficient in both size and execution, in places where C will have a hard time to be optimized (e.g. function pointers in structs).

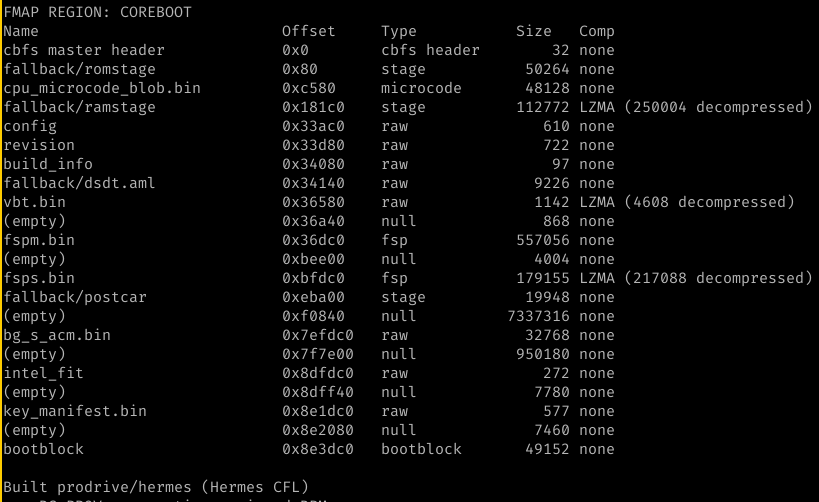

Coreboot on the ASRock E3C246D4I

This blog enty first appeared on the 9esec blog.

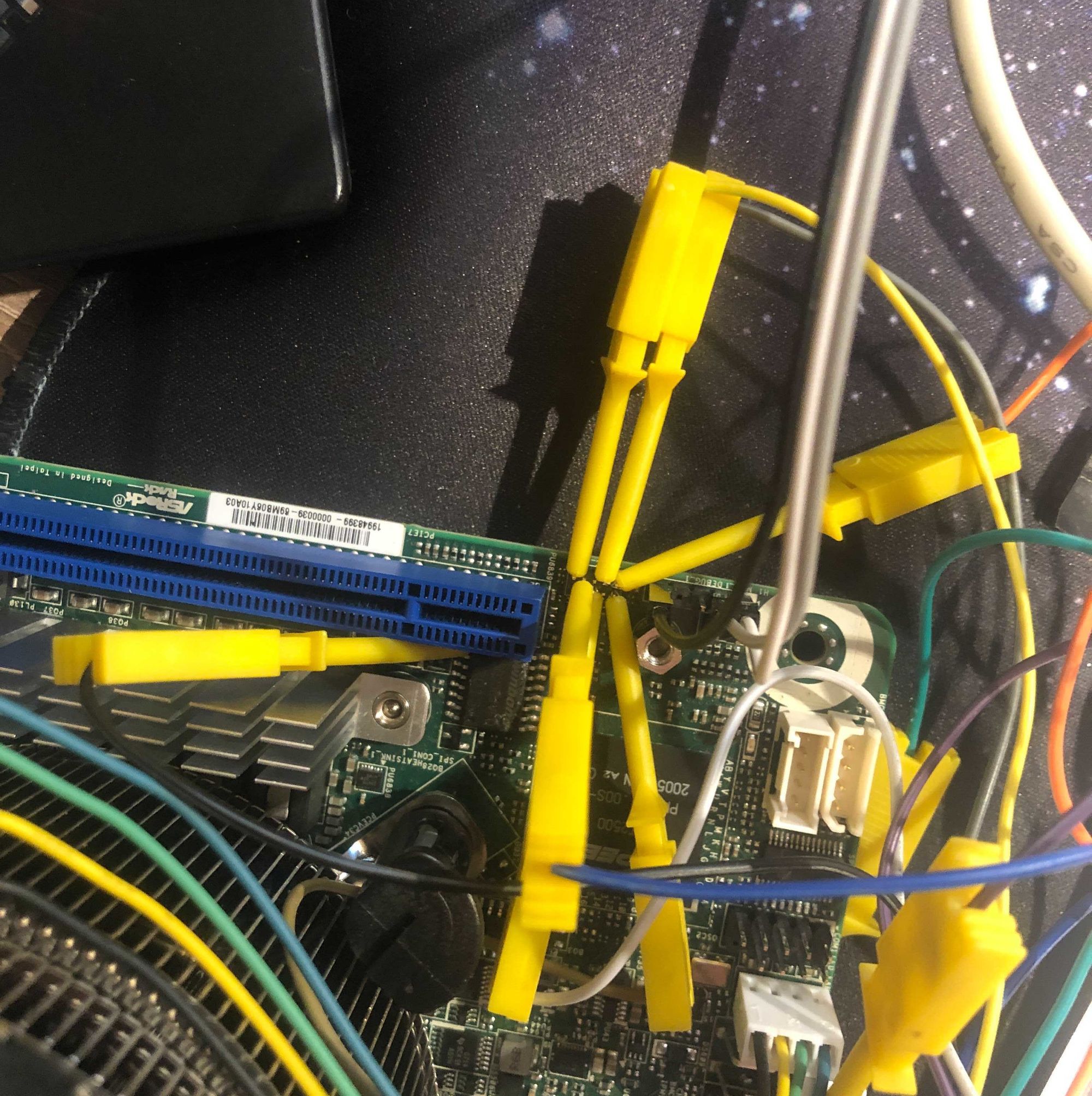

A new toy to play with OpenBMC

I wanted to play around with OpenBMC on a physical board and this article led me to the ASRock E3C246D4I. It's a not overly expensive Intel Coffee Lake board featuring an Aspeed AST2500 BMC. So the first thing I did was to compile OpenBMC. My computer was in for a quite a chore there. It needed to download 11G of sources and compile those. Needless to say this takes a long time on a notebook computer and is best done overnight. I flashed the image via the SPI header next to the BMC flash. I used some mini crocodile clips to do this at first.

Open source cache as ram with Intel Bootguard

This blog enty first appeared on the 9esec blog.

FSP-T in open source projects

X86 CPUs boot up in a very bare state. They execute the first instruction at the top of memory mapped flash in 16 bit real mode. DRAM is not avaible (AMD Zen CPUs are the exception) and the CPU typically has no memory addressable SRAM, a feature which is common on ARM SOCs. This makes running C code quite hard because you are required to have a stack. This was solved on x86 using a technique called cache as ram or CAR. Intel calls this non eviction mode or NEM. You can read more about this here.

Hardware assisted root of trust mechanism and coreboot internals

This blog enty first appeared on the 9esec blog.

I started working for 9elements in October 2020 and my first assignment was to get Intel CBnT working on the OCP Deltalake using coreboot firmware. Intel Converged Bootguard and TXT is a hardware assisted method to set up a root of trust. In this blog post I will discuss some of the changes needed in coreboot to get this working. Setting CBnT up properly was definitely a challenge, but the work did not stop there. So while Intel CBnT provides a method to verify or measure the initial start-up code, it is not enough. You want to trust the code you run from start, the reset vector, to end, typically a bootloader. CBnT only takes care of the start. You have to make sure that each software component trusts the assets it uses and the next program it loads. This concept is called a chain of trust. Now in 2021 I have an assignment that involves supporting the older Intel Bootguard technology. Since Bootguard is very similar to CBnT, I'll also touch on that.

FSP1.1 Braswell TempRaminit problems

Coreboot is migrating platforms from a romcc bootblock to C_ENVIRONMENT_BOOTBLOCK in which Cache-as-Ram is set up in the bootblock.

When migrating Braswell, chromebooks featuring this SOC did not boot anymore while other boards did. Google uses a different FSP binary than the one present in the Intel Github FSP repository.

Previously the romcc bootblock set up caching of the ROM, located microcodes and performed the update before calling FSP TempRaminit.

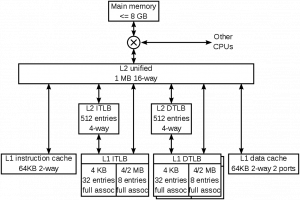

A gentle introduction to Cache-as-Ram on X86

This explains a bit of history on CAR in coreboot and how it works.

Glossary

- CPU cache: CPU cache is a piece of fast memory used by the CPU to cache access to things accessed in the CPU's linear memory space. This includes for DRAM, PCI BARs, the boot flash.

- Cache-as-RAM/CAR: Using not memory mapped CPU cache as execution environment.

- XIP: Execute in place on a memory mapped (read only) medium.

- SRAM: Static Random Access Memory, here: memory mapped memory that needs no initialization.

- ROMCC: A C compiler using only the CPU registers.

Cache-as-Ram, the basics

When an X86 platforms boot, it starts in a pretty bare environment. The first instruction is fetched from the top of the boot medium, which on most x86 platforms is memory mapped below 4G (in 32bit protected mode). Not only do they start in 16bit 'real' mode, most of the hardware starts uninitialized. This includes the dram controller. Another thing about X86 platforms is that they generally don't feature SRAM, static RAM. SRAM for this purpose of this text is a small region of ram that is available without any initialization. Without RAM this leaves the system with just CPU registers and a memory mapped boot medium of which code can be executed in place (XIP) to initialize the hardware.

How to flash coreboot to the thinkpad x60 the proper way

What is so special about the x60 when running vendor bios?

Vendor BIOS write protects its bootblock, which means the lowest 64K of the flash can’t be modified

This is a problem since the first code that runs on the CPU comes from there and if we ever want to run coreboot the cpu must start with coreboot code. This write protection is set in the PBR (protect bios range) registers on the southbridge, there is currently no known way to change them back once they are locked by setting the SPI Configuration Lock-Down bit.